移動(dòng)端

方案網(wǎng)小程序

方案網(wǎng)手機(jī)端

加小編微信入群

發(fā)布成功

移動(dòng)端

方案網(wǎng)小程序

方案網(wǎng)手機(jī)端

加小編微信入群

發(fā)布成功

贊賞金額:

支付金額:5元

支付方式:

贊賞成功!

你的贊賞是對(duì)作者最大的肯定~?

傳統(tǒng)的全芯片 ATPG 正日漸衰退,對(duì)于許多現(xiàn)有的和未來的集成芯片器件來說,一項(xiàng)主要挑戰(zhàn)就是如何為龐大數(shù)量的設(shè)計(jì)創(chuàng)建測(cè)試圖案。先進(jìn)的測(cè)試設(shè)計(jì) (DFT)技術(shù)提供了高效的測(cè)試解決方案,通過提高順序觸發(fā)器的可控性和可觀察性來處理更高的測(cè)試成本、更高的功耗、更高的測(cè)試面積和更小尺寸的引腳數(shù)。反過來,這提高了 SoC 的良率。可靠性和可測(cè)試性是當(dāng)今 ASIC 世界的重要因素。

SoC 只不過是在單個(gè)硅襯底上集成多個(gè)處理器內(nèi)核、微控制器、接口、DSP(數(shù)字信號(hào)處理器)和存儲(chǔ)器的集成電路。在這個(gè)時(shí)代,它是任何數(shù)字系統(tǒng)中最重要的部分之一,因?yàn)樗兄诠?jié)省電力、成本和空間。

內(nèi)核只不過是 SoC 設(shè)計(jì)公司的知識(shí)產(chǎn)權(quán)或 IP 內(nèi)核。SoC 設(shè)計(jì)公司為內(nèi)核提供測(cè)試,而 SoC 設(shè)計(jì)人員提供對(duì)嵌入在芯片上的內(nèi)核的測(cè)試訪問。它是通過插入帶有測(cè)試邏輯的包裝器結(jié)構(gòu)來插入包裝器鏈的層次結(jié)構(gòu)。我們可以最大限度地減少核心測(cè)試問題,并可以減少 SoC 的頂層管腳數(shù)。

本文簡(jiǎn)要介紹了分層 DFT 技術(shù)的重要性,該技術(shù)利用包裝鏈來克服測(cè)試大型 SoC 設(shè)計(jì)的問題。它顯著減少了 ATPG 測(cè)試時(shí)間、內(nèi)存占用和引腳數(shù)。最終,它縮短了上市時(shí)間。

測(cè)試核心包裝器

對(duì)于 DFT,可以在 SoC 級(jí)集成之前單獨(dú)測(cè)試每個(gè)內(nèi)核。在進(jìn)行集成時(shí),當(dāng)它們配置為內(nèi)部測(cè)試模式時(shí),可以單獨(dú)或分組測(cè)試內(nèi)核的內(nèi)部邏輯。但是,當(dāng)配置為外部測(cè)試模式時(shí),可以測(cè)試內(nèi)核的周邊邏輯。通過這樣做,我們主要關(guān)心的是在不同的配置中劃分 SoC 測(cè)試,以大大減少模式生成工作,進(jìn)而減少測(cè)試時(shí)間。

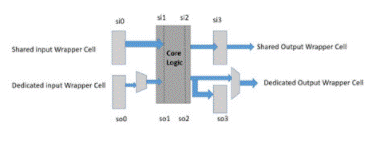

包裝細(xì)胞結(jié)構(gòu)

測(cè)試包裝模式

向內(nèi)或 INTEST 模式

在 INTEST 模式下,通過驅(qū)動(dòng)輸入包裝單元的輸入,我們測(cè)試分區(qū)并通過輸出包裝單元捕獲輸出。這是通過禁用內(nèi)核外部的掃描鏈來完成的。它有助于使用 ATPG 對(duì)分區(qū)核心進(jìn)行隔離測(cè)試。在捕獲期間,輸入包裝器單元使用單獨(dú)的輸入包裝器掃描啟用信號(hào)進(jìn)行移位,這避免了從分區(qū)外部捕獲 x。而輸出包裝單元捕獲分區(qū)的內(nèi)部狀態(tài)。

(圖2:向內(nèi)(測(cè)試)模式)

外向或 EXTEST 模式

在 EXTEST 模式下,封裝器被啟用并配置為驅(qū)動(dòng)和捕獲設(shè)計(jì)之外的數(shù)據(jù)。它本質(zhì)上通過在這種模式下繞過它來禁用內(nèi)部鏈。因此,它也減少了 ATPG 測(cè)試時(shí)間。要測(cè)試分區(qū)和展開邏輯之間的頂層邏輯,我們可以使用這種模式。在捕獲階段,值被分區(qū)外的輸入包裝單元捕獲,并且輸出包裝單元在捕獲期間移動(dòng),以避免從分區(qū)的未驅(qū)動(dòng)的內(nèi)部掃描鏈中捕獲 x。

(圖3:外向(外部)模式)

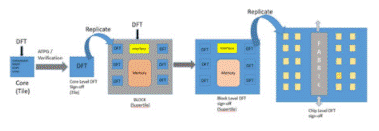

分層 DFT 方法

(圖4:分層DFT實(shí)現(xiàn)(從核心到芯片級(jí)))

大型設(shè)計(jì)問題,如工具內(nèi)存、大 ATPG 運(yùn)行時(shí)間和引腳限制,可以通過分層 DFT 技術(shù)解決。在這種方法中,芯片可以被分成多個(gè)更小的塊或內(nèi)核,可以有效地訪問和處理。由于在核心級(jí)別生成模式,它會(huì)減少引腳數(shù)、內(nèi)存和測(cè)試運(yùn)行時(shí)間。也可以并行運(yùn)行內(nèi)核。

每當(dāng)內(nèi)核配置為內(nèi)部模式時(shí),輸入包裝器就會(huì)啟動(dòng)到內(nèi)核中,并且輸出包裝器會(huì)觀察內(nèi)核輸出。在這種情況下,將測(cè)試包裝器邊界內(nèi)的核心邏輯。所有鏈都連接到壓縮器,它生成可以重新定位到頂層的核心級(jí)別模式。它還有助于合并多個(gè)核心的模式。對(duì)于外部模式,所有包裝鏈都連接到核心邊界,并為頂層生成模式。當(dāng)涉及到全芯片級(jí)時(shí),所有包裝器鏈和頂級(jí)鏈都連接到頂級(jí)壓縮器。

分層 DFT 流

(圖5:測(cè)試訪問機(jī)制)

分層 DFT 的優(yōu)點(diǎn)/缺點(diǎn):

使用分層 DFT 的一些優(yōu)點(diǎn)是:

通過使用自動(dòng)化工具,我們可以在 SoC 級(jí)別組裝核心級(jí)別的鏈。

如果核心層級(jí)鏈?zhǔn)瞧胶獾模敲垂ぞ呔秃苋菀灼胶?SOC 層級(jí)鏈。

通過保持有限數(shù)量的用于掃描鏈的引腳是可以管理的。

它提供了更多的核心級(jí)渠道。

ATPG 運(yùn)行時(shí)間更短,需要更少的內(nèi)存,從而顯著減少了測(cè)試時(shí)間。

一些缺點(diǎn)是:

當(dāng)設(shè)計(jì)包含多個(gè)時(shí)鐘邊沿并在掃描鏈穿過內(nèi)核時(shí)在上升沿和下降沿之間來回遍歷時(shí)導(dǎo)致移位問題時(shí)觸發(fā)觸發(fā)器。為了避免時(shí)序問題,我們必須通過使用鎖定鎖存器來處理內(nèi)核級(jí)別和 SoC 級(jí)別的不同時(shí)鐘域。萬一,在單核級(jí)別出現(xiàn)的時(shí)序問題可能會(huì)損壞所有其他內(nèi)核,因?yàn)殒溤诙鄠€(gè)內(nèi)核中使用。

在本文中,我們探討了包裝器的重要性和包裝器單元的類型。如上所述,包裝器的特征和功能訪問以及包裝器對(duì)不同塊的訪問。我們已經(jīng)看到了使用包裝器的分層 DFT 方法以及圍繞核心邏輯的包裝器單元的互連。最后,我們提到了包裝器的生成以及如何使用包裝器核心來最小化面積和性能影響。分層核心包裝器具有廣泛的工業(yè)用途,我們已經(jīng)展示了使用包裝器單元的結(jié)果。eInfochips為大型 SoC 使用分層 DFT 實(shí)施成功地為其大多數(shù)客戶 提供DFT 解決方案。

關(guān)于我愛方案網(wǎng)

我愛方案網(wǎng)是一個(gè)電子方案開發(fā)供應(yīng)鏈平臺(tái),提供從找方案到研發(fā)采購的全鏈條服務(wù)。找方案,上我愛方案網(wǎng)!在方案超市找到合適的方案就可以直接買,沒有找到就到快包定制開發(fā)。我愛方案網(wǎng)積累了一大批方案商和企業(yè)開發(fā)資源,能提供標(biāo)準(zhǔn)的模塊和核心板以及定制開發(fā)服務(wù),按要求交付PCBA、整機(jī)產(chǎn)品、軟件或IoT系統(tǒng)。更多信息,敬請(qǐng)?jiān)L問http://www.zhaochuanqisf.com